Busqueda de PLA (MOS 906114)

-

Che!!! yo pedi un PLA y voy a terminar siendo ingeniero electronico!!! jejejeej ;)

Ahora en serio, impresionante el nivel tecnico que hay aca, yo no cazo una pero es inevitable el sentimiento de admiración cuando veo tanto conocimiento!

Asi que leo atentamente todo lo que puedo!!!!

Ahora, intentando aplicar el sentido comun, entiendo que la PLA 906114 era un componente algo vulnerable dentro de la arquitectura de una C64.... si esto es asi, tengo altas probabilidades que comprando una C64 fuera de funcionamiento me encuentre con que el componente que quiero reutilizar este en las mismas condiciones que el que poseo... verdad?!?!?!?! o sea quemado... :-/

uummmm sera cuestion de arriesgarse?!?!?!?!

Saludos y gracias a todos!!!!

Alejandro. -

bueno, acompañando lo antedicho por pastbytes, la pla o array logico programable (no programado) contiene internamente una serie de compuertas dispuestas de manera especial de tal forma que cuando estas reciben instrucciones desde el cpu (6510) realizan tareas de habilitacion de los distintos componentes, ya sea roms o puertos externos tipo expancion o cartridge, en la c64 la pla funciona como ampliacion de control para el cpu (6510) y es controlada directamente por el atravez del las direcciones a12,a13,a14,a15 con estos cuatro datos el micro controla las salidas de habilitacion de la pla las cuales permiten el funcionamiento de, por ejemplo las roms (basic,caracteres kernal) atravez de sus pines cs (chip enable, en las rom) para lo cual es necesario que la pla acepte escritura r/w, cosa que es imposible en una eprom ya que es de solo lectura, en tal caso se podria llegar areemplazar con arrays logicos tipo los pal o gal, pero no he visto ninguno por ahora ocupando la posicion de la pla, desde ya que el funcionamiento de la pla es bastante maaaass complejo de lo que comento pero no vendria al caso explicarlo en esta oportunidad, de todas maneras y para tu satisfaccion......

tengo pla 906114 o 82s100 , hablamos. -

Para los no creyentes: LINK

la segunda máquina tiene la PLA reemplazada por una EPROM 27c512

La PLA como ya se dijo, solo tiene compuertas dentro, creo que es una combinación de compuertas AND-NOR, no estoy seguro, de todas maneras, las compuertas estan dispuestas de manera que solo se pueden crear funciones CONVINACIONALES, no sequenciales, como registros, flip-flops, etc.

La pata que esta conectada al R/W del sistema, es una entrada generica de la PLA (I11), no una entrada de lectura/escritura. Y se usa en la PLA para saber si en las secciones donde esta seleccionada ROM, poder leer de la ROM (R/W = 1) o escribir a la RAM directamente por 'debajo', esto permite copiar el contenido de las ROM del sistema sin tener que mover el contenido a otra area de memoria:

Las salidas de la PLA se controlan con 16 entradas:

CHAREN, HIRAM y LORAM: Vienen del puerto de IO incorporado en el procesador y se controlan desde la direccion $0001. Su función es indicar si seleccionar las ROM, RAM o I/O en las distintas areas de memoria ($A000, $D000 y $E000)

GAME y EXROM: Vienen del puerto de expansión y son manejadas por los cartuchos con juegos o utilitarios. GAME es la linea que más altera el mapeado de memoria, desabilitando casi toda la RAM y habilitando la ROM externa creo que en $E000-$F000

VA12, VA13 y VA14: Son las bits más altos del bus de direcciones de video, generadas por una de las CIAs, se usan en la PLA para saber si el chip de video puede ver siempre la ROM de caracteres o no.

BA y AEC: Vienen del chip de video e indican si el bus del sistema esta siendo usado por el procesador o el chip de video (BA), y si el procesador esta 'separado' o no del bus del sistema(AEC).

CAS: Seleccion de Columna de direcciones, viene de la RAM, se usa en la PLA, junto con otras de las entradas para saber si efectivamente seleccionar una columna de direcciones o no (si lo que se va a leer es una ROM o la RAM estatica).

A12 a A15: junto con las otras entradas que ya explique, se usan para seleccionar RAM, ROM o I/O

y R/W que explique al principio.

Ahora las salidas (8):

CASRAM: esta pata va directamente a las patas CAS de las DRAMs internas.

BASIC, KERNAL y CHAROM: van directamente a las patas CS de las ROMS correspondientes.

GR/W: va la pata R/W de la SRAM de color.

I/O: selecciona el bloque de I/O entre $D000 y $DFFF, va, junto con A8, A9, A10 y A11 a 2 decodificadores que seleccionan cada chip por separado (SID, VIC y CIAs) ademas de manejar las dos salidas en el port de expansión I/O1 e I/O2

ROMH y ROML: Seleccionan las ROMs externas, ROMH entre $8000-$9FFF o $E000-$FFFF y ROML entre $A000-$BFFF

-

Si, mientras las entradas sean maximo 16 y las salidas maximo 8, es perfectamente reemplazable por una EPROM, en ese tipo de PLA. Yo lo que explique es justamente para decir que es un metodo bruto, pero que para el caso funciona, es un lujo usar una EPROM para eso, pero si se consigue alguna tirada es una buena solucion, el unico tema es que hay que hacer una placa o algun engendro de cables sobre la placa para adaptar los pines. A la EPROM en este caso no le importa si lo que entra por direcciones son realmente direcciones o lineas de control, para cada combinacion de 16 entradas va a mostrar igualmente una combinacion de 8 salidas.

-

-

bueno, ante la polemica generada por el tema, que de por si esta muy bueno, y sin animo de contradecir a nadie ya que no se trata de un desafio de conocimientos, debo decir: la pla no es una rom, sino un array logico programable, y la 27c512 de la que se habla, no lo es, por lo tanto cuando digo que no se puede reemplazar la pla con esta eprom es por este simple motivo, entiendase reemplazo por sacar la pla y colocar la eprom en el mismo lugar que ocupaba la pla, para lo cual deberian ser identicas pin a pin.

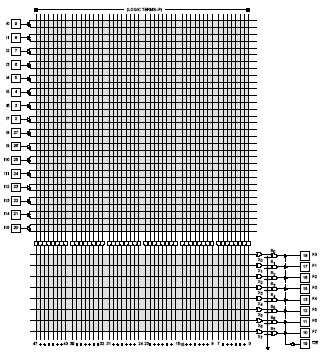

por otro lado la pla 906114-01 es en definitiva una matriz que resuelve operaciones booleanas, tiene 16 entradas (i0-i16) desde las cuales, cuando se le escribe datos (por esto lo de r/w) internamente resuelve las ecuaciones entre sus and y or de arquitectura invertida resultando en 48 productos los cuales manejan las 8 salidas de datos del integrado (f0-f7) por otro lado a la eprom 27c256 no se la puede escribir (ya que es de solo lectura) y por esto cuando se presentan datos en sus 16 lineas de direccion, no entradas, lo unico que se hace es apuntar a una posicion de memoria para obtener los datos guardados alli y reflejarlos en sus 8 salidas, emulando asi el resultado de las operaciones que la pla real realiza internamente, de esta forma con una eprom 27c512 que opere a 50ns se puede emular la pla grabando en ella el resultado de los 48 productos haciendolos coincidir

con los 16 bits de datos de entrada de la pla que como ya dije en la epron seran direcciones de memoria, cosa que repito dado que cuando hable de r/w en la pla no me referia al pin r/w de la misma ya que este es solo una de las 16 entradas y corresponde a I11, de todos modos, si, es posible emular (no reemplazar) la pla con una eprom 27c512 para la cual tengo el firmware de emulacin de productos, y los cambios en los pines que se deben realizar para luego poder colocarla en en zocalo de la pla original, pero no me parecio oportuno comentarlo dado el caso de que cuento en mi haber con pla originales y lo que se pidio en este caso era una pla, de hecho fue mas facil llevarle una a karageorgos que programar una eprom.

con respecto a las direcciones (o mapeo de memoria) es bastante mas complejo de lo explicado pero para comentar alguna de las nombradas $E000-$FFFF son las posiciones donde se aloja el contenido de la kernal rom y contiene el sistema operativo, cuando la c64 se enciende el contenido de la kernal es cargado en estas posiciones y al ejecutarse realiza tareas como, limpiar la ram, obtener la info de perifericos de entrada salida, preparar el vic (procesador de video) para su uso, setear varios punteros, chequear el autoarranque desde cartuchos en el puerto de expancion y arrancar el interprete basic si no hay cartucho enchufado, ademas ningun cartucho se aloja en estas direcciones salvo que el mismo reemplace al sistema operativo, y las ultimas posiciones $FFFA-$FFFE son usadas por el cpu (6510) como vectores de hardware por ejemplo $FFFA que apunta a las rutinas de interupcion del micro (NMI), o $FFFC (o mas conocido como sys64738) que ocupa el vector de reset, y $FFFE que apunta al vector de IRQ, y como dije al principio la idea no es corregir a nadie si no compartir info y aprender de la info que suministran otros usuarios.

(pero cuando se arman estos debates se pone bueno jajajajaja.) -

-

Los cartuchos que ocupan el area $e000-$ffff son los llamados 'ultimax', porque son los que fueron hechos para la Commodore Max Machine.

Estos cartuchos ponen a '0' la linea GAME, y hacen que la C64 cambie su configuracion de memoria a la misma de la Max Machine, con solo 4KB de RAM, y dos areas de ROM externa en $e000-$ffff y $a000-$bfff -

Bueno... al nivel de esta conversación lo que tengo para avisar solo podría titularse como "Avisos Parroquiales" jejejejej

YA TENGO LA PLA Y LA C64 YA VIVE NUEVAMENTE!!!

Gracias Sr, Electroeject!!!

Listo! no estorbo mas a los que saben!!! ;)

Saludos y gracias a todos!

Alejandro. -

si, si the _woz, tiene razon, me habia olvidado de la max, desde ya que esa maquina era una rareza muy poco vista, y con sus solo 2,5 kb de memoria no le quedaba otra que obtener el systema operativo desde un cartucho, por eso cuando ese cartucho se coloca en la comodore 64 reemplaza las posiciones de la kernal y desde ya que reemplaza al systema operativo de la c64 por el de la max, muy buen dato.